|

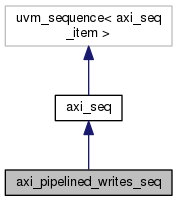

AXI muckbucket

|

|

AXI muckbucket

|

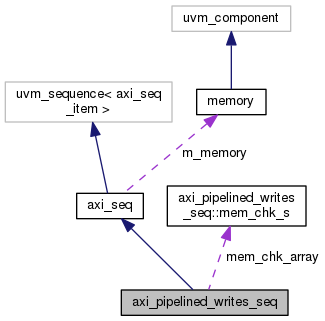

Writes to memory over AXI, backdoor readback. More...

Classes | |

| struct | mem_chk_s |

Public Member Functions | |

| uvm_object_utils (axi_pipelined_writes_seq) axi_seq_item write_item[] | |

| new (string name="axi_pipelined_writes_seq") | |

| Constructor. More... | |

| task | body () |

| Does all the work. More... | |

| void | response_handler (uvm_sequence_item response) |

| Handles write responses, including verifying memory via backdoor reads. More... | |

| uvm_object_utils (axi_seq) const int clearmemory=0 | |

| void | set_transaction_count (int count) |

| How many transactions? More... | |

| bit | compare_items (ref axi_seq_item write_item, ref axi_seq_item read_item) |

| Compares the write-item with the corresponding read_item. More... | |

Public Attributes | |

| int | transaction_id |

| event | writes_done |

| mem_chk_s | mem_chk_array [*] |

| const int | window_size = 0x1_0000 |

| int | xfers_to_send = 1 |

| bit | valid [] |

| bit< 2:0 > | max_burst_size |

| int | xfers_done =0 |

| memory | m_memory |

Writes to memory over AXI, backdoor readback.

Writes are pipelined so multiple in flight at once.

miscompares are flagged.

Definition at line 35 of file axi_pipelined_writes_seq.svh.

| struct axi_pipelined_writes_seq::mem_chk_s |

Definition at line 48 of file axi_pipelined_writes_seq.svh.

| Class Members | ||

|---|---|---|

| bit< ADDR_WIDTH-1:0 > | laddr | |

| bit< ADDR_WIDTH-1:0 > | uaddr | |

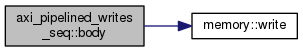

| task axi_pipelined_writes_seq::body | ( | ) |

Does all the work.

Verifies read back data with written data.

two modes: Serial, Write_addr, then write, then resp. Repeat Parallel - Multiple write_adr, then multiple write_data, then multiple resp, repeat

Definition at line 131 of file axi_pipelined_writes_seq.svh.

References ADDR_WIDTH, e_WRITE, ID_WIDTH, axi_pipelined_writes_seq::mem_chk_s::laddr, axi_seq::m_memory, mem_chk_array, transaction_id, axi_pipelined_writes_seq::mem_chk_s::uaddr, axi_seq::valid, axi_seq::window_size, memory::write(), writes_done, axi_seq::xfers_done, and axi_seq::xfers_to_send.

|

inherited |

Compares the write-item with the corresponding read_item.

THis isn't the same as a do_compare() method in the axi_seq_item because the readback is depenent on which burst_type Although it could probably exist as aseperate method in the seqitem.

| write_item | - the original item |

| read_item | - the item after memory readback |

........................

Definition at line 115 of file axi_seq.svh.

References e_FIXED, e_INCR, e_WRAP, and axi_seq::max_burst_size.

| axi_pipelined_writes_seq::new | ( | string | name = "axi_pipelined_writes_seq" | ) |

Constructor.

Doesn't actually do anything except call parent constructor

Definition at line 113 of file axi_pipelined_writes_seq.svh.

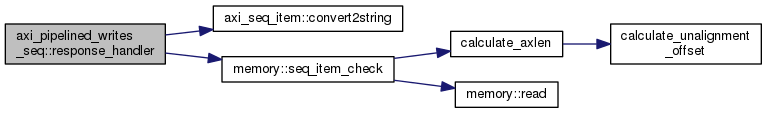

| automatic void axi_pipelined_writes_seq::response_handler | ( | uvm_sequence_item | response | ) |

Handles write responses, including verifying memory via backdoor reads.

Definition at line 67 of file axi_pipelined_writes_seq.svh.

References ADDR_WIDTH, axi_seq_item::cmd, axi_seq_item::convert2string(), e_WRITE_RESPONSE, axi_seq_item::id, axi_pipelined_writes_seq::mem_chk_s::laddr, axi_seq::m_memory, mem_chk_array, memory::seq_item_check(), axi_pipelined_writes_seq::mem_chk_s::uaddr, axi_seq::xfers_done, and axi_seq::xfers_to_send.

|

inherited |

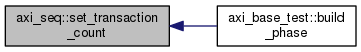

How many transactions?

This method sets how many transactions to send (Write Address, Write Data, Write Response) is one traction (Read Address, Read Data) is one transaction

| count | - how many transactions to send |

Definition at line 92 of file axi_seq.svh.

References axi_seq::xfers_to_send.

Referenced by axi_base_test::build_phase().

|

pure virtualinherited |

| axi_pipelined_writes_seq::uvm_object_utils | ( | axi_pipelined_writes_seq | ) |

|

inherited |

Definition at line 48 of file axi_seq.svh.

Referenced by axi_sequential_reads_seq::body(), axi_sequential_writes_seq::body(), axi_pipelined_reads_seq::body(), body(), axi_pipelined_reads_seq::response_handler(), and response_handler().

|

inherited |

Definition at line 44 of file axi_seq.svh.

Referenced by axi_seq::compare_items(), and axi_seq::new().

| mem_chk_s axi_pipelined_writes_seq::mem_chk_array[*] |

Definition at line 53 of file axi_pipelined_writes_seq.svh.

Referenced by body(), and response_handler().

| int axi_pipelined_writes_seq::transaction_id |

Definition at line 41 of file axi_pipelined_writes_seq.svh.

Referenced by body().

|

inherited |

Definition at line 42 of file axi_seq.svh.

Referenced by axi_sequential_writes_seq::body(), axi_pipelined_reads_seq::body(), and body().

|

inherited |

Definition at line 39 of file axi_seq.svh.

Referenced by axi_sequential_reads_seq::body(), axi_sequential_writes_seq::body(), axi_pipelined_reads_seq::body(), and body().

| event axi_pipelined_writes_seq::writes_done |

Definition at line 45 of file axi_pipelined_writes_seq.svh.

Referenced by body().

|

inherited |

Definition at line 46 of file axi_seq.svh.

Referenced by axi_sequential_reads_seq::body(), axi_pipelined_reads_seq::body(), body(), axi_pipelined_reads_seq::response_handler(), and response_handler().

|

inherited |

Definition at line 40 of file axi_seq.svh.

Referenced by axi_sequential_reads_seq::body(), axi_sequential_writes_seq::body(), axi_pipelined_reads_seq::body(), body(), axi_pipelined_reads_seq::response_handler(), response_handler(), and axi_seq::set_transaction_count().

1.8.11

1.8.11