|

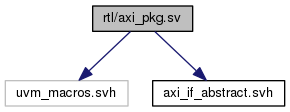

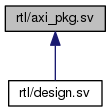

AXI muckbucket

|

|

AXI muckbucket

|

Go to the source code of this file.

Classes | |

| struct | axi_seq_item_aw_vector_s |

| This packed struct is used to send write address channel information between the DUT and TB. More... | |

| struct | axi_seq_item_w_vector_s |

| This packed struct is used to send write data channel information between the DUT and TB. More... | |

| struct | axi_seq_item_b_vector_s |

| This packed struct is used to send write response channel information between the DUT and TB. More... | |

| struct | axi_seq_item_ar_vector_s |

| This packed struct is used to send read address channel information between the DUT and TB. More... | |

| struct | axi_seq_item_r_vector_s |

| This packed struct is used to send read data channel information between the DUT and TB. More... | |

Namespaces | |

| axi_pkg | |

| enums, defines, typedefs needed in AXI | |

Typedefs | |

| typedef bit< AXI_SEQ_ITEM_AW_NUM_BITS-1:0 > | axi_seq_item_aw_vector_t |

| Bit vector containing packed write address channel values. More... | |

| typedef bit< AXI_SEQ_ITEM_W_NUM_BITS-1:0 > | axi_seq_item_w_vector_t |

| Bit vector containing packed write data channel values. More... | |

| typedef bit< AXI_SEQ_ITEM_B_NUM_BITS-1:0 > | axi_seq_item_b_vector_t |

| Bit vector containing packed write response channel values. More... | |

| typedef bit< AXI_SEQ_ITEM_AR_NUM_BITS-1:0 > | axi_seq_item_ar_vector_t |

| Bit vector containing packed read address channel values. More... | |

| typedef bit< AXI_SEQ_ITEM_R_NUM_BITS-1:0 > | axi_seq_item_r_vector_t |

| Bit vector containing packed read data channel values. More... | |

Enumerations | |

| enum | burst_size_t { e_1BYTE = 0b000, e_2BYTES = 0b001, e_4BYTES = 0b010, e_8BYTES = 0b011, e_16BYTES = 0b100, e_32BYTES = 0b101, e_64BYTES = 0b110, e_128BYTES = 0b111 } |

| Size of beat in bytes. (How many bytes of the data bus are used each beat(clk). More... | |

| enum | burst_type_t { e_FIXED = 0b00, e_INCR = 0b01, e_WRAP = 0b10, e_RESERVED = 0b11 } |

| Does the address stay fixed, increment, or wrap during the burst? More... | |

| enum | response_type_t { e_OKAY = 0b00, e_EXOKAY = 0b01, e_SLVERR = 0b10, e_DECERR = 0b11 } |

| Write response values. More... | |

Functions | |

| bit< C_AXI_ADDR_WIDTH-1:0 > | calculate_burst_aligned_address (input bit< C_AXI_ADDR_WIDTH-1:0 > address, input bit< 2:0 > burst_size) |

| calculate burst_size aligned address More... | |

| bit< C_AXI_ADDR_WIDTH-1:0 > | calculate_bus_aligned_address (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input int bus_size) |

| calculate bus-siz aligned address More... | |

| bit< C_AXI_LEN_WIDTH-1:0 > | calculate_axlen (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input bit< 2:0 > burst_size, input shortint burst_length) |

| calculate awlen or arlen More... | |

| byte | calculate_unalignment_offset (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input byte burst_size) |

| calculate how unaligned the address is from the burst size More... | |

| void | calculate_wrap_boundary (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input bit< 2:0 > burst_size, input shortint burst_length, output bit< C_AXI_ADDR_WIDTH-1:0 > Lower_Wrap_Boundary, output bit< C_AXI_ADDR_WIDTH-1:0 > Upper_Wrap_Boundary) |

| calculate the wrap boundaries for a given burst More... | |

| bit< C_AXI_ADDR_WIDTH-1:0 > | get_next_address (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input bit< 2:0 > burst_size, input shortint burst_length, input bit< 1:0 > burst_type, input int beat_cnt, input int lane, input int data_bus_bytes) |

| Get next address for reading/writing to memory. More... | |

| void | get_beat_N_byte_lanes (input bit< C_AXI_ADDR_WIDTH-1:0 > addr, input bit< 2:0 > burst_size, input shortint burst_length, input bit< 1:0 > burst_type, input int beat_cnt, input int data_bus_bytes, output int Lower_Byte_Lane, output int Upper_Byte_Lane, output int offset) |

| return byte lanes that contain valid data More... | |

Variables | |

| parameter | C_AXI_ID_WIDTH = params_pkg::AXI_ID_WIDTH |

| parameter | C_AXI_DATA_WIDTH = params_pkg::AXI_DATA_WIDTH |

| parameter | C_AXI_ADDR_WIDTH = params_pkg::AXI_ADDR_WIDTH |

| parameter | C_AXI_LEN_WIDTH = params_pkg::AXI_LEN_WIDTH |

| localparam int | AXI_SEQ_ITEM_AW_NUM_BITS = $bits(axi_seq_item_aw_vector_s) |

| localparam int | AXI_SEQ_ITEM_W_NUM_BITS = $bits(axi_seq_item_w_vector_s) |

| localparam int | AXI_SEQ_ITEM_B_NUM_BITS = $bits(axi_seq_item_b_vector_s) |

| localparam int | AXI_SEQ_ITEM_AR_NUM_BITS = $bits(axi_seq_item_ar_vector_s) |

| localparam int | AXI_SEQ_ITEM_R_NUM_BITS = $bits(axi_seq_item_r_vector_s) |

| struct axi_seq_item_aw_vector_s |

This packed struct is used to send write address channel information between the DUT and TB.

Packed structs are emulator friendly

Definition at line 113 of file axi_pkg.sv.

| Class Members | ||

|---|---|---|

| logic< C_AXI_ADDR_WIDTH-1:0 > | awaddr |

Starting burst address |

| logic< 1:0 > | awburst |

address burst mode. fixed, incrementing, or wrap |

| logic< 3:0 > | awcache |

Memory type. See AXI spec Memory Type A4-65 |

| logic< C_AXI_ID_WIDTH-1:0 > | awid |

Write address ID tag - A matching write response ID, bid, will be expected |

| logic< C_AXI_LEN_WIDTH-1:0 > | awlen |

Length, in beats/clks, of the matching write data burst |

| logic< 0:0 > | awlock |

Used for locked transactions in AXI3 |

| logic< 2:0 > | awprot |

Protected transaction. AXI4 only |

| logic< 3:0 > | awqos |

Quality of service. AXI4 only |

| logic | awready |

Slave is ready to receive write address channel information |

| logic< 2:0 > | awsize |

beat size. How many bytes wide are the beats in the write data transfer |

| logic | awvalid |

Values on write address channel are valid and won't change until awready is recieved |

| struct axi_seq_item_w_vector_s |

This packed struct is used to send write data channel information between the DUT and TB.

Packed structs are emulator friendly

Definition at line 141 of file axi_pkg.sv.

| Class Members | ||

|---|---|---|

| logic< C_AXI_DATA_WIDTH-1:0 > | wdata |

Write Data |

| logic< C_AXI_ID_WIDTH-1:0 > | wid |

Write ID tag. AXI3 only |

| logic | wlast |

Write last. Indicates last beat in a write burst. |

| logic< C_AXI_DATA_WIDTH/8-1:0 > | wstrb |

Write strobe. Indicates which byte lanes hold valid data. |

| logic | wvalid |

Write valid. Values on write data channel are valid and won't change until wready is recieved |

| struct axi_seq_item_b_vector_s |

This packed struct is used to send write response channel information between the DUT and TB.

Packed structs are emulator friendly

Definition at line 162 of file axi_pkg.sv.

| Class Members | ||

|---|---|---|

| logic< C_AXI_ID_WIDTH-1:0 > | bid |

Write Response ID tag |

| logic< 1:0 > | bresp |

Write Response.Indicates status of the write data transaction. |

| struct axi_seq_item_ar_vector_s |

This packed struct is used to send read address channel information between the DUT and TB.

Packed structs are emulator friendly

Definition at line 178 of file axi_pkg.sv.

| Class Members | ||

|---|---|---|

| logic< C_AXI_ADDR_WIDTH-1:0 > | araddr |

Starting burst address |

| logic< 1:0 > | arburst |

address burst mode. fixed, incrementing, or wrap |

| logic< 3:0 > | arcache |

Memory type. See AXI spec Memory Type A4-65 |

| logic< C_AXI_ID_WIDTH-1:0 > | arid |

Read address ID tag - A matching read data ID, rid, will be expected |

| logic< C_AXI_LEN_WIDTH-1:0 > | arlen |

Length, in beats/clks, of the matching read data burst |

| logic< 0:0 > | arlock |

Used for locked transactions in AXI3 |

| logic< 2:0 > | arprot |

Protected transaction. AXI4 only |

| logic< 3:0 > | arqos |

Quality of service. AXI4 only |

| logic | arready |

Slave is ready to receive read address channel information |

| logic< 2:0 > | arsize |

beat size. How many bytes wide are the beats in the write data transfer |

| logic | arvalid |

Values on read address channel are valid and won't change until arready is recieved |

| struct axi_seq_item_r_vector_s |

This packed struct is used to send read data channel information between the DUT and TB.

Packed structs are emulator friendly

Definition at line 205 of file axi_pkg.sv.

| Class Members | ||

|---|---|---|

| logic< C_AXI_DATA_WIDTH-1:0 > | rdata |

Write Data |

| logic< C_AXI_ID_WIDTH-1:0 > | rid |

Read ID tag. |

| logic | rlast |

Read last. Indicates last beat in a read burst. |

| logic< 1:0 > | rresp |

Read Response.Indicates status of the read data transfer (of the same beat). |

| logic | rvalid |

Write valid. Values on read data channel are valid and won't change until rready is recieved |

| typedef bit<AXI_SEQ_ITEM_AR_NUM_BITS-1:0> axi_seq_item_ar_vector_t |

Bit vector containing packed read address channel values.

Definition at line 197 of file axi_pkg.sv.

| typedef bit<AXI_SEQ_ITEM_AW_NUM_BITS-1:0> axi_seq_item_aw_vector_t |

Bit vector containing packed write address channel values.

Definition at line 132 of file axi_pkg.sv.

| typedef bit<AXI_SEQ_ITEM_B_NUM_BITS-1:0> axi_seq_item_b_vector_t |

Bit vector containing packed write response channel values.

Definition at line 171 of file axi_pkg.sv.

| typedef bit<AXI_SEQ_ITEM_R_NUM_BITS-1:0> axi_seq_item_r_vector_t |

Bit vector containing packed read data channel values.

Definition at line 218 of file axi_pkg.sv.

| typedef bit<AXI_SEQ_ITEM_W_NUM_BITS-1:0> axi_seq_item_w_vector_t |

Bit vector containing packed write data channel values.

Definition at line 154 of file axi_pkg.sv.

| enum burst_size_t |

Size of beat in bytes. (How many bytes of the data bus are used each beat(clk).

Definition at line 76 of file axi_pkg.sv.

| enum burst_type_t |

Does the address stay fixed, increment, or wrap during the burst?

Definition at line 89 of file axi_pkg.sv.

| enum response_type_t |

Write response values.

Definition at line 98 of file axi_pkg.sv.

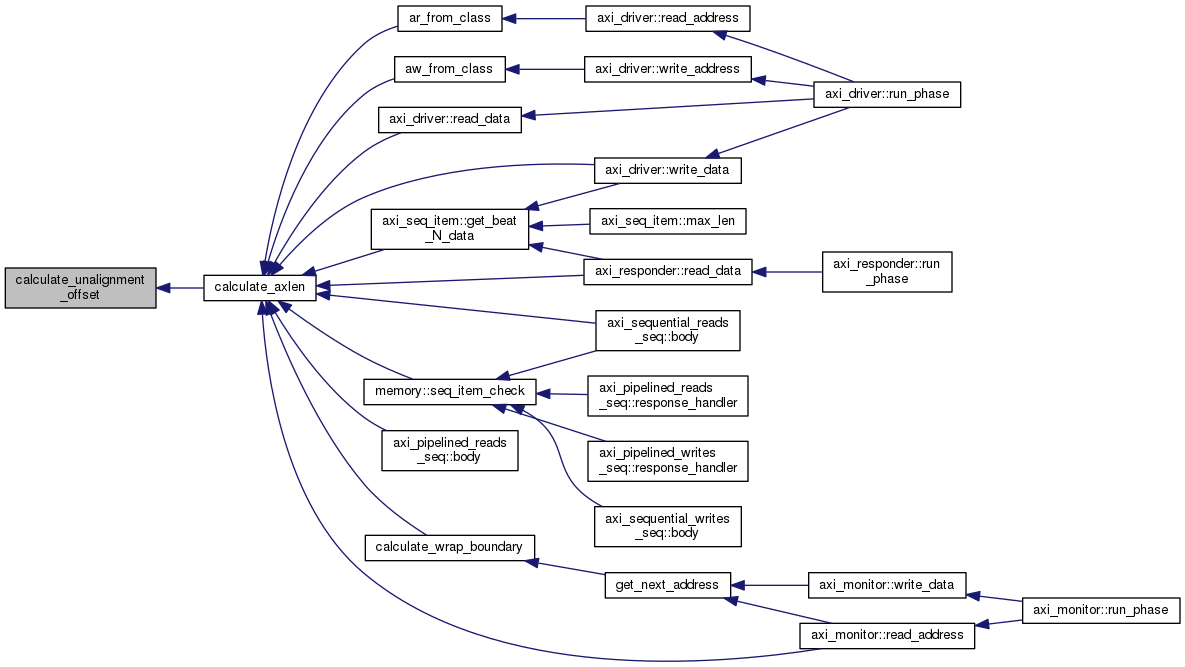

| bit<C_AXI_LEN_WIDTH-1:0> calculate_axlen | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input bit< 2:0 > | burst_size, | ||

| input shortint | burst_length | ||

| ) |

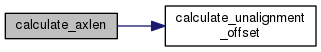

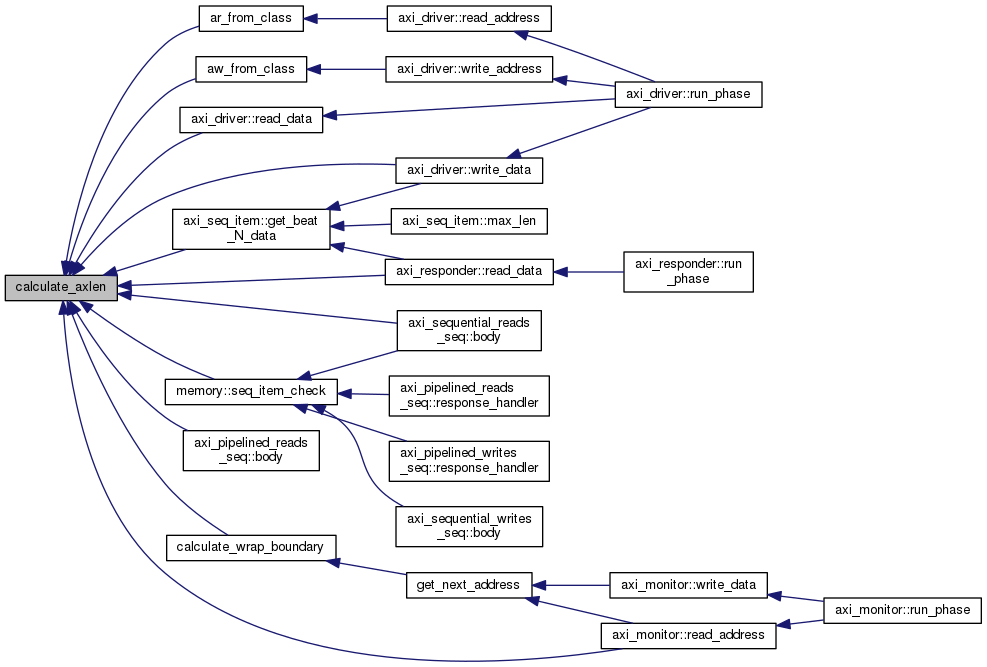

calculate awlen or arlen

Calculate the number of beats -1 for a burst. Subtract one because awlen and arlen are one less than the transfer count. awlen=0, means 1 beat.

| addr | - starting address |

| burst_size | - how many bytes wide is the beat |

| burst_length | - how many bytes long is the burst |

Definition at line 320 of file axi_pkg.sv.

References C_AXI_LEN_WIDTH, and calculate_unalignment_offset().

Referenced by ar_from_class(), aw_from_class(), axi_sequential_reads_seq::body(), axi_pipelined_reads_seq::body(), calculate_wrap_boundary(), axi_seq_item::get_beat_N_data(), axi_monitor::read_address(), axi_driver::read_data(), axi_responder::read_data(), memory::seq_item_check(), and axi_driver::write_data().

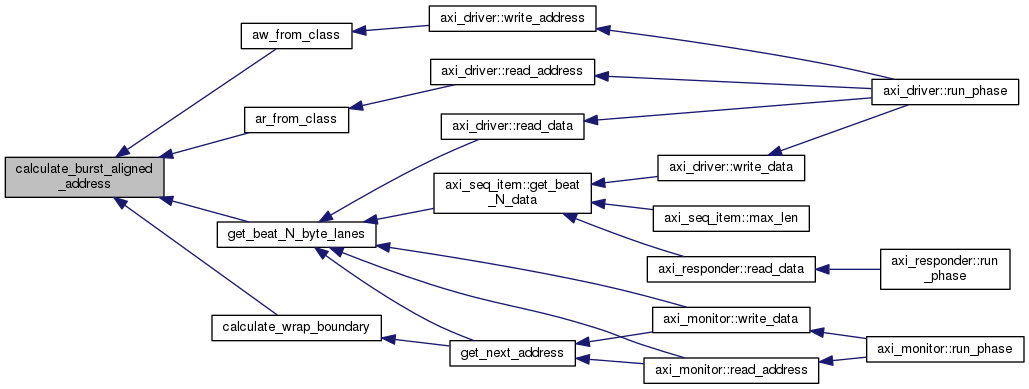

| bit<C_AXI_ADDR_WIDTH-1:0> calculate_burst_aligned_address | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | address, |

| input bit< 2:0 > | burst_size | ||

| ) |

calculate burst_size aligned address

The AXI function to calculate aligned address is: Aligned_Address = (Address/(2**burst_size)*(2**burst_size) Zeroing out the bottom burst_size bits does the same thing which is much more eaily synthesizable.

| address | - starting address |

| burst_size | - how many bytes wide is the beat |

Definition at line 230 of file axi_pkg.sv.

References C_AXI_ADDR_WIDTH, e_128BYTES, e_16BYTES, e_1BYTE, e_2BYTES, e_32BYTES, e_4BYTES, e_64BYTES, and e_8BYTES.

Referenced by ar_from_class(), aw_from_class(), calculate_wrap_boundary(), and get_beat_N_byte_lanes().

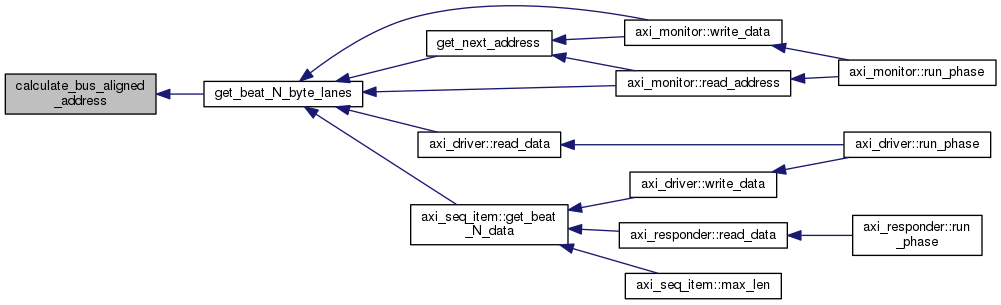

| bit<C_AXI_ADDR_WIDTH-1:0> calculate_bus_aligned_address | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input int | bus_size | ||

| ) |

calculate bus-siz aligned address

The AXI function to calculate aligned address is: Aligned_Address = (Address/(2**bus_size)*(2**bus_sze) Zeroing out the bottom burst_size bits does the same thing which is much more eaily synthesizable.

| addr | - starting address |

| bus_size | - how many bytes wide is the bus |

Definition at line 272 of file axi_pkg.sv.

References C_AXI_ADDR_WIDTH, e_128BYTES, e_16BYTES, e_1BYTE, e_2BYTES, e_32BYTES, e_4BYTES, e_64BYTES, and e_8BYTES.

Referenced by get_beat_N_byte_lanes().

| byte calculate_unalignment_offset | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input byte | burst_size | ||

| ) |

calculate how unaligned the address is from the burst size

| addr | - starting address |

| burst_size | - how many bytes wide is the beat |

Definition at line 374 of file axi_pkg.sv.

References e_128BYTES, e_16BYTES, e_1BYTE, e_2BYTES, e_32BYTES, e_4BYTES, e_64BYTES, and e_8BYTES.

Referenced by calculate_axlen().

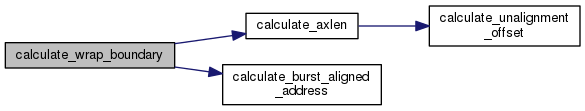

| void calculate_wrap_boundary | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input bit< 2:0 > | burst_size, | ||

| input shortint | burst_length, | ||

| output bit< C_AXI_ADDR_WIDTH-1:0 > | Lower_Wrap_Boundary, | ||

| output bit< C_AXI_ADDR_WIDTH-1:0 > | Upper_Wrap_Boundary | ||

| ) |

calculate the wrap boundaries for a given burst

| addr | - starting address |

| burst_size | - how many bytes wide is the beat |

| burst_length | - how many bytes is the burst |

Definition at line 406 of file axi_pkg.sv.

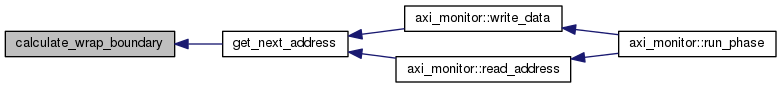

References C_AXI_ADDR_WIDTH, calculate_axlen(), and calculate_burst_aligned_address().

Referenced by get_next_address().

| void get_beat_N_byte_lanes | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input bit< 2:0 > | burst_size, | ||

| input shortint | burst_length, | ||

| input bit< 1:0 > | burst_type, | ||

| input int | beat_cnt, | ||

| input int | data_bus_bytes, | ||

| output int | Lower_Byte_Lane, | ||

| output int | Upper_Byte_Lane, | ||

| output int | offset | ||

| ) |

return byte lanes that contain valid data

given the beat number and how wide the bus is, return which lanes to get data from and also what offset from start address to write to.

| addr | - starting address |

| burst_size | - how many bytes wide is the beat |

| burst_length | - how many bytes is the burst |

| burst_type | - Fixed, Incrementing or Wrap |

| beat_cnt | which beat in the burst, starting at 0. |

| data_bus_bytes | - how wide is the bus (the driver/responder can get this from the interface |

| Lower_Byte_Lane | - Lower valid byte lane |

| Upper_Byte_Lane | - Upper valid byte lane |

| offset | - offset from Start_Address. Can be used to write to memory. |

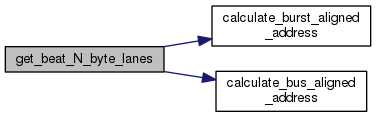

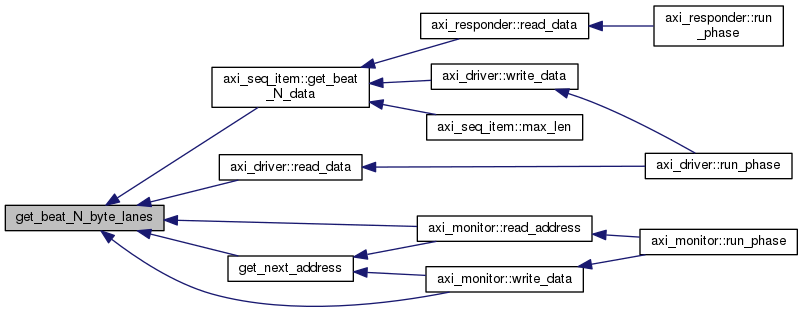

Definition at line 538 of file axi_pkg.sv.

References calculate_burst_aligned_address(), calculate_bus_aligned_address(), and e_FIXED.

Referenced by axi_seq_item::get_beat_N_data(), get_next_address(), axi_monitor::read_address(), axi_driver::read_data(), and axi_monitor::write_data().

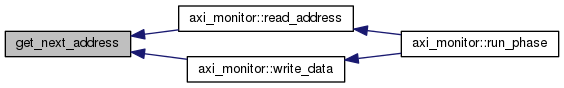

| bit<C_AXI_ADDR_WIDTH-1:0> get_next_address | ( | input bit< C_AXI_ADDR_WIDTH-1:0 > | addr, |

| input bit< 2:0 > | burst_size, | ||

| input shortint | burst_length, | ||

| input bit< 1:0 > | burst_type, | ||

| input int | beat_cnt, | ||

| input int | lane, | ||

| input int | data_bus_bytes | ||

| ) |

Get next address for reading/writing to memory.

Takes into account burst_type. IE: e_FIXED, e_INCR, e_WRAP This function is stateful. When called it updates an internal variable that holds the current address.

| addr | - starting address |

| burst_size | - how many bytes wide is the beat |

| burst_length | - how many bytes is the burst |

| burst_type | - Fixed, Incrementing or Wrap |

| beat_cnt | - beat count the memory address corresponds to. Used with lane. |

| lane | - lane thememory address correspons to. Usedwith beat_cnt |

| data_bus_bytes | - how wide is the bus? |

Definition at line 447 of file axi_pkg.sv.

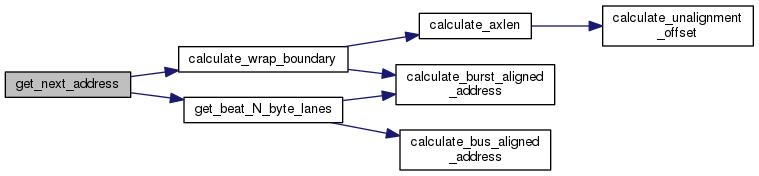

References C_AXI_ADDR_WIDTH, calculate_wrap_boundary(), e_FIXED, e_INCR, e_WRAP, and get_beat_N_byte_lanes().

Referenced by axi_monitor::read_address(), and axi_monitor::write_data().

| localparam int AXI_SEQ_ITEM_AR_NUM_BITS = $bits(axi_seq_item_ar_vector_s) |

Used to calculate the length of the bit vector containing the packed read address struct

Definition at line 193 of file axi_pkg.sv.

| localparam int AXI_SEQ_ITEM_AW_NUM_BITS = $bits(axi_seq_item_aw_vector_s) |

Used to calculate the length of the bit vector containing the packed write address struct

Definition at line 128 of file axi_pkg.sv.

| localparam int AXI_SEQ_ITEM_B_NUM_BITS = $bits(axi_seq_item_b_vector_s) |

Used to calculate the length of the bit vector containing the packed write response struct

Definition at line 167 of file axi_pkg.sv.

| localparam int AXI_SEQ_ITEM_R_NUM_BITS = $bits(axi_seq_item_r_vector_s) |

Used to calculate the length of the bit vector containing the packed read data struct

Definition at line 214 of file axi_pkg.sv.

| localparam int AXI_SEQ_ITEM_W_NUM_BITS = $bits(axi_seq_item_w_vector_s) |

Used to calculate the length of the bit vector containing the packed write data struct

Definition at line 150 of file axi_pkg.sv.

| parameter C_AXI_ADDR_WIDTH = params_pkg::AXI_ADDR_WIDTH |

bit width of address bus. Valid values:

Definition at line 59 of file axi_pkg.sv.

Referenced by axi_if(), calculate_burst_aligned_address(), calculate_bus_aligned_address(), calculate_wrap_boundary(), and get_next_address().

| parameter C_AXI_DATA_WIDTH = params_pkg::AXI_DATA_WIDTH |

bit width of data bus. Valid values:

Definition at line 48 of file axi_pkg.sv.

Referenced by axi_if().

| parameter C_AXI_ID_WIDTH = params_pkg::AXI_ID_WIDTH |

bit width of the ID fields

Definition at line 41 of file axi_pkg.sv.

Referenced by axi_if().

| parameter C_AXI_LEN_WIDTH = params_pkg::AXI_LEN_WIDTH |

bit width of awlen and arlen bus. Valid values:

Definition at line 65 of file axi_pkg.sv.

Referenced by axi_if(), and calculate_axlen().

1.8.11

1.8.11